MEMS器件封装无铅锡膏深圳福英达分享:MEMS 器件低应力封装技术

MEMS器件封装无铅超微锡膏深圳福英达分享:MEMS 器件低应力封装技术

锡膏_焊锡膏_超微焊料_助焊膏生产商-深圳福英达是一家集锡膏、锡胶及合金焊粉产、销、研与服务于一体的综合型锡膏供应商, 是工信部焊锡粉标准制定主导单位,产品涵盖超微无铅印刷锡膏,超微无铅点胶锡膏,超微无铅喷印锡膏,超微无铅针转移锡膏,超微无铅免洗焊锡膏,超微无铅水洗锡膏,高温焊锡膏,中高温焊锡膏,低温焊锡膏,7号锡膏、8号锡膏,低温超微锡胶,中高温锡胶,各向异性导电胶,金锡锡膏,金锡锡粉,多次回流锡膏,激光锡膏,微间距助焊胶,高温无铅锡膏,低温锡铋银锡膏,低温高可靠性锡膏,无铅焊膏锡铋银锡膏/胶,SAC305锡膏,低温高可靠性锡膏&锡胶,无银&锡铜锡膏,超微焊粉,Low alpha无铅焊料,Low alpha高铅焊料,SMT粉,定制焊料。拥有从合金焊粉到应用产品的完整产品线,可制造T2-T10全尺寸超微合金焊粉的电子级封装材料。

摘要:封装是微机电系统(micro-electro-mechanical system, MEMS)研发过程中的最重要的环节之一。封装决定了MEMS 器件的可靠性以及成本,是MEMS 器件实用化和商业化的关键。然而,封装过程中引入的残余应力会造成MEMS 器件输出信号的偏移,同时封装应力随时间逐渐变化,严重影响MEMS 器件的可靠性以及长期稳定性。因此,降低封装应力是实现MEMS 器件高性能和高稳定性的关键要素。简要分析了芯片级封装过程中MEMS 器件封装应力产生的机理,详细介绍了目前国内外降低应力封装技术和方法,并对于MEMS 器件低应力封装技术作出了总结和展望。

关键词:MEMS;传感器;低应力封装;可靠性;长期稳定性

0 引言

微机电系统(micro-electro-mechanical systems,MEMS)是一种将电和机械集成的微器件或微系统。MEMS 沿用集成电路(integrated circuit,IC)的微米/纳米微加工工艺,是集合微型结构、微型传感器、微型执行器以及信号处理、控制、通信等功能于一体的完整且复杂的系统。MEMS 具有体积小、功耗低、性能好,与IC 制作工艺兼容性好等优点,在消费电子、工业控制、医疗器械、信息通信、武器装备以及国防安全等领域中得到了越来越广泛的应用。封装技术决定了MEMS 器件的成本和可靠性,是MEMS 普遍实用化的基础和实现商业化成功的关键因素。一方面,封装成本制约了MEMS 商业化发展。由于MEMS 器件种类多样,同时大多数MEMS器件的封装都是面向特定应用,一种制造工艺和封装工艺很难简单的移植到其他MEMS 器件开发中,工业上MEMS 封装没有统一标准,这极大增加了MEMS 器件开发的技术难度和成本,一般MEMS仅封装成本就占总成本的70% 以上。另一方面,MEMS 封装的可靠性制约MEMS 普遍实用化。与IC不同,MEMS 一般包含精密可动微结构,MEMS 封装不仅需要提供必要的电学和其他物理场的互联,还需对MEMS 结构以及电连接等提供支持和保护,使之免受外部环境的干扰或破坏。封装中面临着结构优化、工艺条件的选择、热力学效应和多物理场耦合等问题。研究表明,在MEMS 系统中发生的可靠性问题50%来自电子封装过程。

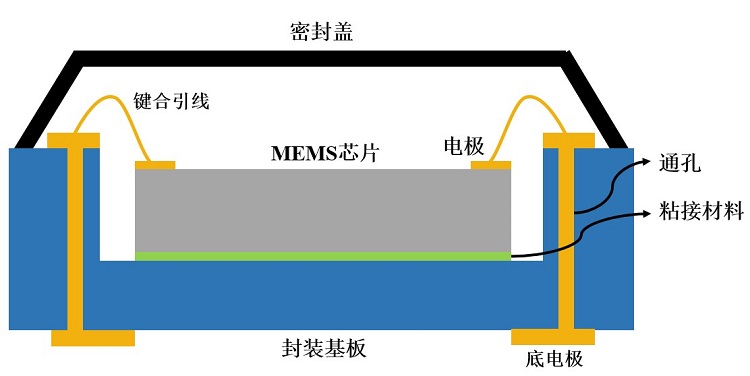

MEMS 封装过程会引入额外的应力,严重影响MEMS 器件的稳定性和可靠性。封装应力是由于MEMS 器件材料与封装材料之间热膨胀系数(coefficient of thermal expansion,CTE)不匹配而产生。MEMS 芯片级封装主要用于实现芯片电学连通,同时保护芯片免受外界环境的影响。MEMS 芯片级封装一般包括芯片粘贴、引线键合、封盖和气密焊接等关键基础工艺,典型的MEMS 芯片级封装截面示意图如图1 所示。

图1 典型MEMS芯片级封装截面示意图

Fig.1 Schematic diagram of a typical MEMSchip scale package

研究表明,芯片粘接工艺是芯片级封装中最主要的应力来源,MEMS 芯片衬底材料、粘接材料和封装基板之间的材料性能不匹配,特别是MEMS 器件衬底硅与封装基板之间材料CTE 失配从而产生较大的封装应力。封装应力会直接造成芯片的翘曲和变形,进而影响MEMS 器件的性能。对于一些应力敏感的MEMS 器件如压阻传感器、压力传感器来说,封装过程产生应力直接作用于器件本身,直接影响其测量结果的准确性。对于谐振器件或者惯性器件,如MEMS 谐振器、加速度计和陀螺仪等而言,由于封装应力引起的结构几何形变和等效刚度变化会改变器件的谐振频率 和品质因子(quality factor,Q),从而造成传感器的输出信号如刻度因子和零偏等产生漂移。当器件上的应力过大时,会导致MEMS 器件在界面区域产生裂纹、分层甚至失效,从而破坏MEMS 器件的互连,引起失效或引发长期的可靠性问题。

控制和减少封装应力对于提高对于应力敏感的MEMS 器件如压力传感器、谐振器以及惯性器件的性能可靠性和长期稳定性具有重要的意义。因此,本文主要聚焦于芯片粘接工艺,分析了芯片粘接工艺中封装应力的产生机理,同时从封装材料、封装工艺以及封装结构方面详细介绍了目前芯片粘接工艺中降低封装应力和提高应力敏感MEMS 器件性能和稳定性的方法,并对于MEMS 器件低应力封装技术进行了总结和展望。

1 芯片粘接工艺中应力产生机理

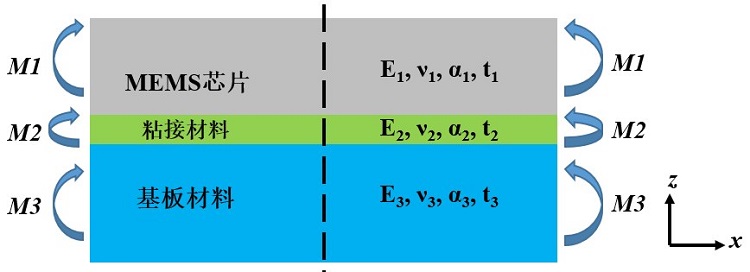

芯片粘接工艺是通过粘接材料将芯片连接到封装基板上的工艺过程。该工艺一般分为施胶、贴片和固化3 个步骤,首先将MEMS 芯片通过粘接材料固定于封装基板,之后加热整体结构至固化温度,最后冷却至室温即完成芯片粘接。从固化温度冷却到室温的过程中,由于MEMS 衬底、粘接材料层和封装基板之间的材料性能不匹配而产生了的残余热应力,导致MEMS 封装结构发生形变。在芯片粘接过程中,MEMS 芯片、粘接材料和封装基板典型3 层结构如图2 所示。

图2 芯片粘接过程中典型的3层结构

Fig.2 Typical three-layer structure in die attachment process

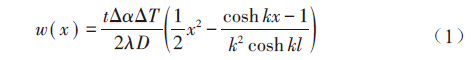

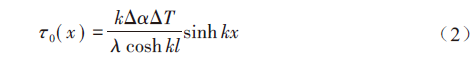

根据Suhir 理论,从纯弯曲过程中弯曲力矩与弯曲曲率的关系出发,采用数值分析的方法推导出了芯片粘接过程中封装应力的解。在此3 层结构中,每层材料的厚度和力学性能决定了整体的翘曲或挠度w( x) 如下式表示:

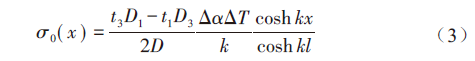

芯片粘接过程中的剪切应力τ0( x),可以精确地表示为:

芯片粘接过程中的剥离应力σ0( x),可以精确地表示为:

其中,Ei 为第i 层材料的杨氏模量;Gi 为第i 层材料的剪切模量;vi 为第i 层材料的泊松比;αi 为第i 层材料的热膨胀系数;ti 为第i 层材料的厚度;t 为多层结构总的厚度;Δα = α3 - α1,为芯片与封装基板材料热膨胀系数的差值;ΔT = To - Tref,为工作温度To 与固化温度Tref 的差值;

由式(1)、(2)和(3)可知,封装热应力与冷却过程中固化温度与工作温度差值以及芯片与封装基板材料CTE 的差值成正比,同时封装应力与各层材料的弹性模量、泊松比以及厚度相关。

2 低应力芯片粘接

基于封装应力产生的机理,为了降低MEMS 封装过程中的封装应力,目前研究主要从封装材料、封装工艺以及封装结构等方面做出优化,将针对上述3个方面介绍和分析低应力芯片粘接方法。

2.1 封装材料优化

在芯片粘接工艺中MEMS 芯片材料、粘接材料和基板材料之间物理性能的差异是封装应力的来源。因此,封装材料的选择和优化有利于降低封装应力。

2.1.1 粘接材料

常用的芯片粘接材料主要包括环氧树脂、共晶焊料和掺金属玻璃粘接剂等。环氧树脂应用于芯片的低温粘接,由于环氧树脂导热和导电性较差,通常在环氧树脂中加入金属粉末(如金和银等)用于提高环氧树脂的导热性和导电性;而共晶焊料和掺金属玻璃粘接剂主要应用于芯片的高温粘接,适用于大功率器件,其粘接质量较好,但成本较高。表1 为部分粘接材料的物理性质,从中可以看出环氧树脂的固化温度低于掺银玻璃粘接剂以及共晶焊料,采用环氧树脂粘接材料所引起的封装应力更小。

表1 部分粘接材料物理性质

Table 1 Physical properties of some adhesive materials

Walwadka 等研究了芯片粘接工艺中粘接材料的杨氏模量和CTE 对于封装应力引起的芯片形变的影响。结果表明,粘接材料的CTE 对于封装应力影响不大,粘接材料的弹性模量越小,应力越小。降低粘接材料的固化温度和杨氏模量能明显降低MEMS器件封装应力。基于此,K?niger 等提出了一种基于丙烯酸酯的低温固化、低杨氏模量以及具有高粘结强度的低应力粘接材料。该新型粘接材料杨氏模量低至0.1GPa,同时固化温度为降至100℃ ,有效降低了MEMS 封装应力。目前,德国的Henkel、美国的ZYMET 和EPOXY 等公司已经开发出了用于MEMS低应力封装的环氧树脂,低杨氏模量粘接材料已经实现商业化。然而,降低粘接材料弹性模量只适用于环氧树脂型粘接材料,低杨氏模量的环氧树脂中并未掺入金属粉末,因此其导热和导电性能很差,不适用于高可靠性封装应用。

锡银铜SAC锡膏 锡银铜 SACS锡膏 锡铋银SnBiAg锡膏 锡铋银锑SnBiAgSb锡膏 锡铋银SnBiAgX锡膏 锡铋SnBi锡膏 BiX 锡膏 金锡AuSn锡膏 锡锑SnSb锡膏 含铅 SnPb锡膏 各向异性导电锡胶 微间距助焊胶

2.1.2 基板材料

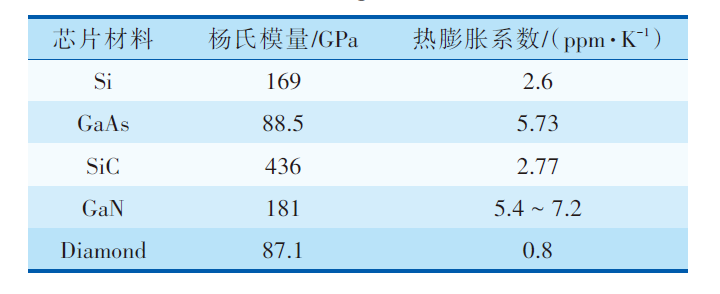

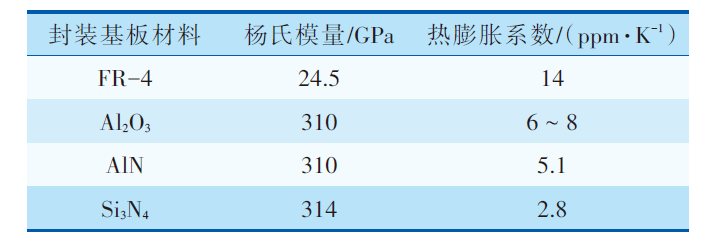

封装基板材料与MEMS 芯片材料之间的CTE 差值是封装应力的最主要来源,减小基板与芯片之间的CTE 的差值能有效减小封装应力。常用MEMS 芯片材料的物理性质如表2 所示,表3 为常用的封装基板材料物理性质参数。

表2 常用MEMS 芯片材料物理性质

Table 2 Physical properties of commonly usedMEMS chip materials

表3 常用封装基板材料物理性质

Table 3 Physical properties of commonly usedsubstrate materials

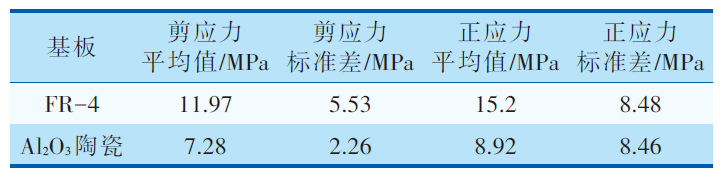

孙志国等探究了FR-4(印刷电路板)基板和Al2O3陶瓷基板在芯片粘接固化过程中MEMS 硅芯片表面的应力,结果如表4所示。结果表明采用与硅CTE 差值较小的陶瓷基板能显著降低封装应力。合理选择与MEMS 芯片材料CTE 相近的封装材料能有效降低封装应力,然而,在实际MEMS 器件研发中,很难使得封装基板材料和MEMS 芯片材料CTE 完美匹配,封装应力不可避免。此外,低热膨胀系数的封装基板材料价格昂贵,不利于低成本MEMS 器件的商业化应用。

表4 采用不同封装基板材料下封装应力

Table 4 Packaging stress under different substrate materials

2.2 封装工艺优化

芯片粘接工艺中,封装应力主要是在固化冷却过程中产生,优化芯片粘贴工艺能减小封装应力。

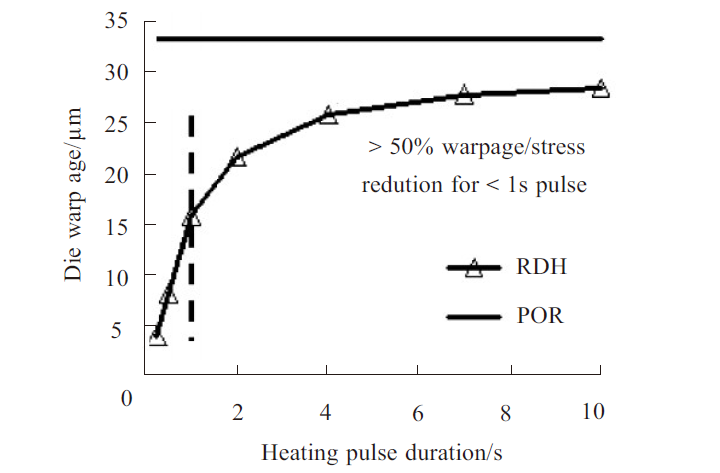

Frutschy 等提出一种基于热脉冲技术局部快速加热芯片和粘接材料的方法用于降低封装应力。通过控制热脉冲功率和时间使得芯片和粘接材料快速达到固化温度,由于热传导时间较短,此时基板的温度相对较低,在固化降温时,冷却过程中基板与芯片结构之间因热位移失配而产生的应力可相应减少。图3为此方法与传统热固化工艺下芯片翘曲结果对比,可以看出,当加热时间小于1 s 时,芯片的整体翘曲与传统工艺方法相比降低了50%。此方法能有效降低封装应力,但由于工艺步骤复杂和成本高昂,限制了其广泛应用。

图3 传统粘接工艺和不同脉冲加热时间粘接工艺下芯片翘曲对比

Fig.3 Comparison of chip warpage using traditional dieattachment and pulse laser heating bonding process

Walwadkar 等提出了一种热循环固化工艺方法用于降低封装应力。粘接材料为银玻璃粘接剂。在完成芯片粘接后,采用热循环(1~400℃)的方法对整体芯片结构进行热处理,实验结果表明封装应力在热循环过程中明显下降。银玻璃胶在热循环下产生了应力松弛,热循环起到了降低封装应力的作用。然而,该方法仅适用于银玻璃粘接材料。

2.3 封装结构优化

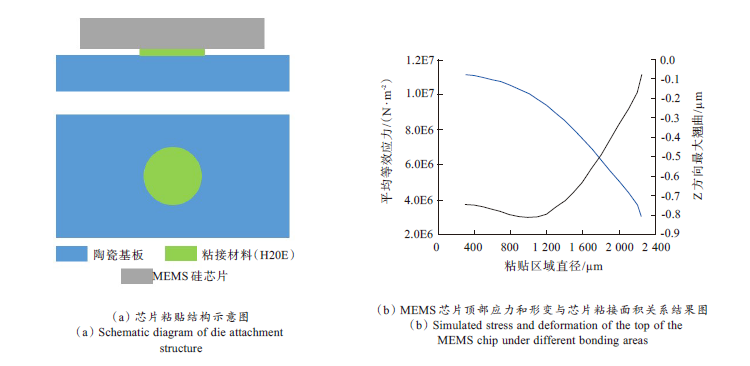

优化封装结构是降低MEMS 封装应力中最常用的方法。优化封装结构可以改变封装应力的分布和传导,进而减小应力对于MEMS 器件的影响。芯片和封装材料之间的封装应力主要通过粘接材料来传递。图4 为仿真芯片粘接工艺中改变粘接面积下MEMS 芯片顶面的应力变化,可以看出,随着粘接面积减小,MEMS 芯片所受到的封装应力越小。Li 等通过减少粘接面积的方式直接降低了封装应力对于MEMS 加速度计性能的影响,该低应力封装方式方法已经成功应用于摩托罗拉MEMS 器件的批量封装。

图4 仿真芯片粘接工艺中改变粘接面积下MEMS芯片顶面的应力变化

Fig.4 Simulated stress on the top surface of the chip under different bonding areas in die attachment

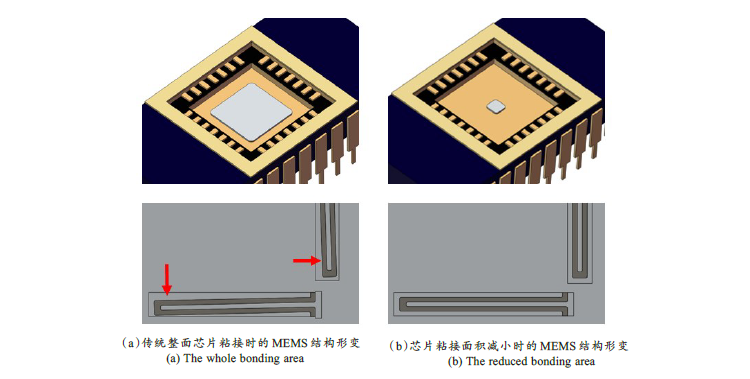

加州大学欧文分校Prikhodko 等研究了采用Au-Sn 共晶合金焊料进行芯片粘接时,粘接面积变化下封装应力对于MEMS 陀螺仪形变和性能的影响。实验对比了整面粘贴和较小粘接面积两种情况下芯片粘接后陀螺仪器件的结构形变,如图5 所示。整面粘贴结构下器件梁结构明显发生变形,如图5(a)所示。减小芯片粘接面积后MEMS 器件结构形变如图5(b)所示,MEMS 陀螺仪的梁结构几乎没有形变。说明减小粘接面积能明显降低MEMS 器件结构的应力和形变。同时,通过减小陀螺仪粘接面积,谐振式陀螺仪器件的频率漂移减小至20%,有效提高了MEMS 陀螺仪的稳定性和可靠性。

图5 不同粘接面积下由封装应力导致MEMS器件结构形变

Fig.5 The structural deformation of MEMS devices induced by packaging stress under different bonding areas

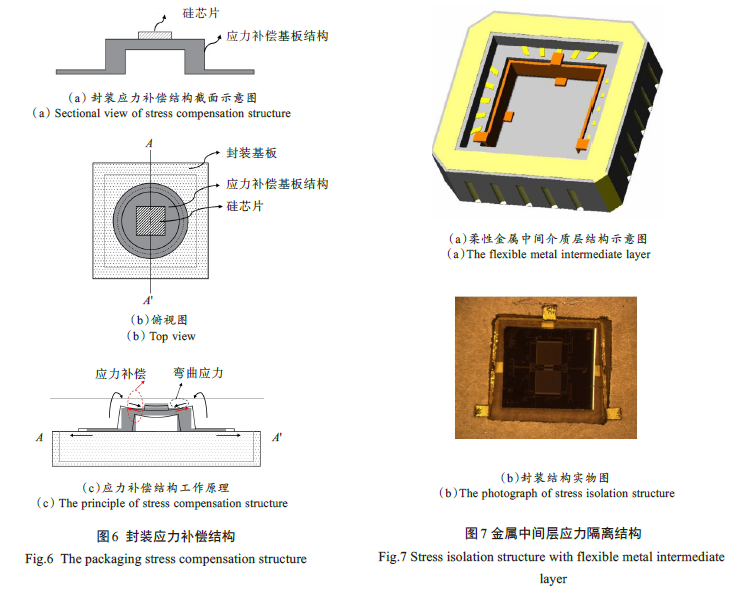

日本横河电机公司Samejima 等提出了一种带热应力补偿基板结构用于补偿MEMS 压力传感器的封装应力,如图6 所示,其封装结构如图6(a)和(b)所示。该应力补偿结构为带凹腔的基板结构。其工作原理如图6(c)所示,将硅芯片粘贴在热应力补偿结构的基板上时,当基板结构受热膨胀时,热应力补偿结构下端受到拉应力而使上端凹陷,此结构变化会使芯片下端产生压应力,此压应力会抵消芯片因热膨胀而产生的拉应力;同理,当基板受冷收缩时,热应力补偿结构下端受到压应力,热应力补偿结构上端突起,在芯片下端产生拉应力,会补偿芯片因冷收缩而产生的压应力,从而起到降低应力的作用。采用传统芯片粘接工艺下,由封装应力所导致的压力传感器输出误差高达250 με/K,而采用热应力补偿结构的压力传感器输出误差降至6 με/K,该方法有效降低了封装应力对于压力传感器输出误差的影响。

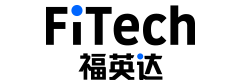

Marinis 等通过在陶瓷基板上加入柔性金属中间介质层结构用于降低芯片粘接应力,其结构如图7所示。中间层结构可以减少芯片与陶瓷基板之间的热膨胀失配,起到应力隔离的作用。与传统粘贴方式相比,加入柔性金属中间层结构下由于应力引起的芯片翘曲降低了5 倍左右,大幅度减少了粘接过程引起的应力。

Schr?der 等提出了一种双面引线键合法用于MEMS 陀螺仪低应力封装。该方法利用双面引线键合工艺替代了传统芯片粘接工艺。MEMS 芯片是通过封装外框引出数条金属引线,实现电学导通的同时,将MEMS 芯片的上、下端面进行固定。该方法通过导线点固定MEMS 芯片,大幅度降低了与基板之间的粘接面积,能起到良好的应力隔离作用。采用双面引线键合方式下由应力所引起的MEMS 陀螺仪芯片形变明显减小,说明此方法能有效降低由应力引起的芯片翘曲。通过优化键合线的数量,该方法能减少MEMS 陀螺仪的共振模式,降低了杂模态对于MEMS 陀螺仪性能的影响。然而,此方法增加了工艺的复杂性,不利于实现大规模批量制造。

3 结论

MEMS 封装涉及机械、材料、力学、热物理及电子信息等多学科与多领域交叉,粘接过程中材料选择、工艺和封装结构的不合理都会导致封装应力的产生。封装应力严重影响对于应力敏感器件如MEMS 压力传感器、谐振器以及惯性器件的稳定性和可靠性。本文同时从封装材料、封装工艺以及封装结构方面详细介绍了目前芯片粘接工艺中降低封装应力的方法,目前降低封装应力的方法仍然存在一些局限性,低应力封装材料只适用于特定的应用场合,封装工艺以及结构普遍存在结构复杂,成本较高等缺点。

随着MEMS 器件应用的不断发展,工业中对于应力敏感的MEMS 器件的精度和稳定性要求不断提高。低成本和通用性的低应力封装技术仍是一个挑战。未来降低封装应力的手段主要集中于两个方面,一是新型封装材料的研发,应致力于开发通用性好的低应力粘接材料以及与MEMS 芯片材料CTE 完美匹配的封装基板材料,才能从根本上减小封装应力;二是封装结构的进一步优化,主要集中于应力隔离结构和应力补偿结构的开发。在此基础上,需具体考虑不同种类MEMS 传感器的结构和工作原理,同时兼顾封装方法的成本和复杂性,才能提出对应的降低应力的有效方法。

作者:吴忠烨,杨尚书,吴国强

(武汉大学工业科学研究院)

深圳市福英达20年以来一直深耕于微电子与半导体封装材料行业。致力于为业界提供先进的焊接材料和技术、优质的个性化解决方案服务与可靠的焊接材料产品。提供包括LED微间距低温封装锡膏锡胶、LED微间距中温高温封装锡膏锡胶、LED微间距低温高强度锡膏锡胶、倒装芯片封装焊料、FPC柔性模块封装锡膏锡胶、植球/晶圆级植球助焊剂、凸点制作锡膏、PCBA锡膏锡胶、车用功率模块封装锡膏锡胶、车载娱乐封装锡膏锡胶、车用LED封装焊料、车载MEMS封装焊料、轨道交通用IGBT封装锡膏锡胶、基带芯片系统级封装锡膏锡胶、存储芯片高可靠封装锡膏锡胶、射频功率器件封装锡膏锡胶、多次回流封装锡膏锡胶、物联网安全芯片封装焊料、支付芯片系统级封装焊料、物联网身份识别封装焊料、MEMS微机电系统封装锡膏锡胶、射频功率器件锡膏锡胶、芯片封装锡膏锡胶、摄像头模组封装专用锡胶、简化封装工艺免洗锡膏/锡胶、高可靠性水洗锡膏、低温高强度锡膏/锡胶、便于返修的锡膏产品、高性价比锡膏方案、高可靠高温Au80Sn20焊料、高可靠Low alpha 高铅封装焊料、高可靠水洗焊料、医疗设备高可靠性封装锡膏锡胶、医疗设备系统级封装焊料、复杂结构激光焊接锡膏锡胶、精密结构低温封装焊料解决方案。以及mLED新型显示各向异性导电胶、mLED新型显示微间距焊接助焊胶、mLED新型显示高强度细间距锡胶、mLED新型显示微间距低温焊料、mLED新型显示微间距SAC305锡膏、SMT低温元器件贴装锡胶、SMT低温元器件贴装锡膏、SMTSAC305系列锡膏、SMT微间距助焊胶、Low α无铅焊料、SiP水洗锡膏、SiP无铅无银焊料、Low α高铅焊料、MEMS水洗激光锡膏、MEMS低温高可靠性锡胶、MEMS低温高可靠锡膏、MEMS多次回流焊料、MEMSAu80Sn20金锡焊膏、功率器件高铅焊料、功率器件水洗锡膏、功率器件无铅锡膏、功率器件Au80Sn20金锡锡膏解决方案。

返回列表

返回列表